# dialog

#### **Cordless Voice Module**

FINΔI

# **General description**

The SC14CVMDECT SF is a member of the Cordless Module family with integrated radio transceiver and baseband processor in a single package. It is designed for hosted and embedded cordless voice and data applications in the DECT frequency band. Its simple to use API commands allow easy setup of a wireless link between two or more nodes.

#### **Features**

- Supports EU-DECT (CAT-iq V2.0, v3.0 partly), DECT6.0 for North America and Japan DECT

- ETSI (EU-DECT) and FCC (DECT 6.0) certified

- J-DECT pre-certified

- ETSI 300 444 (DECT GAP) compliant

- Up to 64 Portable Parts or ULE devices registered per Fixed Part

- UART interface to external host

- Controllable via API command set

- Supports voice and data

- RF range: 1870 MHz to 1930 MHz

- Receiver sensitivity < -93 dBm

- Transmit power

- EU: 23 dBm: 1881 MHz 1897 MHz

USA: 20 dBm: 1921 MHz 1928 MHz

- JP: 23 dBm: 1895 MHz 1903 MHz

- Antenna embedded, supports external antennas

- Contains both PP and FP functionality

- Program memory available for custom software

- Supports both internal and external (hosted) applications

- Power supply voltage: 2.1 V to 3.45 V

- Supports NiMH and Alkaline batteries

- Small form factor (19.6 mm x 18.0 mm x 2.7 mm)

- Operating temperature range: -40 °C to +85 °C

# **Applications**

- Cordless intercom

- Cordless baby monitor

- Wireless data applications up to 54 kbit/s

- FP supports ULE sensors and actuators

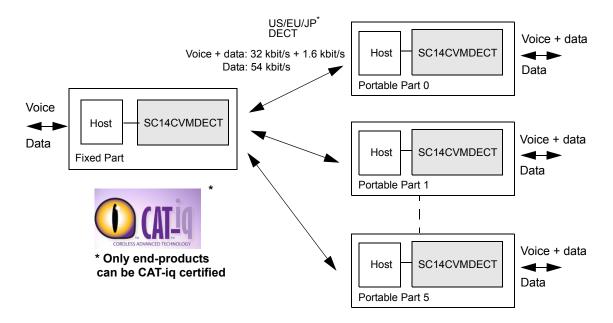

### System diagram

#### FINΔI

# **Table of Contents**

| 1.0 | Connection diagram 4                |     | 4.9 BATTERY MANAGEMENT                        | . 21 |

|-----|-------------------------------------|-----|-----------------------------------------------|------|

|     | 1.1 PIN DESCRIPTION 5               | ;   | 4.10 PROTOCOL STACK                           | . 21 |

| 2.0 | Introduction 8                      | •   | 4.10.1 DECT TBR22                             | . 21 |

| 2.0 |                                     |     | 4.10.2 Out-of-Range handling                  | . 22 |

|     | 2.1 SCOPE 8                         |     | 4.10.3 Preamble antenna diversity             | . 22 |

|     | 2.2 REFERENCES                      |     | 4.10.4 Broadcasting messages                  | . 22 |

|     | 2.3 GLOSSARY AND DEFINITIONS 8      | }   | 4.10.5 IWU to IWU messaging                   | 22   |

| 3.0 | Cordless Voice Module functions 10  | )   | 4.11 REGISTRATION                             | . 22 |

|     | 3.1 MODULE HARDWARE                 | )   | 4.11.1 Handling product identities            | . 22 |

|     | 3.2 SOFTWARE CONTROL                | )   | 4.11.2 Deregistration                         | . 23 |

|     | 3.3 DECT PROTOCOL STACK             | )   | 4.12 PCM INTERFACE                            | . 23 |

|     | 3.4 PORTABLE PART CONFIGURATION     |     | 4.12.1 PCM Interface for FP                   | . 23 |

|     | 3.5 FIXED PART CONFIGURATION        |     | 4.12.2 PCM_FSC frequency                      | . 23 |

|     | 3.6 VOICE COMMUNICATION             | )   | 4.12.3 Length of PCM_FSC                      | . 23 |

|     | 3.7 LIGHT DATA APPLICATION          |     | 4.12.4 Start position of FSC                  | 23   |

|     | 3.8 LU10 DATA APPLICATION           | !   | 4.12.5 PCM clock frequency                    | . 23 |

|     | 3.9 GENERAL FEATURES                | ļ   | 4.12.6 PCM data mode                          | . 24 |

|     |                                     |     | 4.12.7 PCM Interface for PP                   | 27   |

| 4.0 | Functional description              | i   | 4.13 ANTENNA OPERATION                        | 27   |

|     | 4.1 UART INTERFACE                  |     | 4.13.1 Internal antenna only                  | . 28 |

|     | 4.2 VES (VIRTUAL EEPROM STORAGE) 15 |     | 4.13.2 Internal and external antenna with FAD | 28 ( |

|     | 4.2.1 VES layout                    | 5.0 | CAT-iq                                        | 29   |

|     | 4.2.2 VES access by MCU 15          | )   |                                               |      |

|     | 4.3 AUDIO CONFIGURATIONS            | i   | 5.1 INTRODUCTION                              |      |

|     | 4.3.1 Audio connection              | i   | 5.2 CAT-IQ PROFILE OVERVIEW                   |      |

|     | 4.4 AUDIO ROUTING                   | ;   | 5.2.1 Supported main features                 | 29   |

|     | 4.4.1 FP audio routing 17           | 6.0 | Register descriptions                         | . 30 |

|     | 4.4.2 FP audio level adjustment 17  | 7 0 | Specifications                                | 36   |

|     | 4.4.3 PP audio routing 17           |     | 7.1 GENERAL                                   |      |

|     | 4.4.4 PP audio codec adjustment 17  | •   | 7.2 ABSOLUTE MAXIMUM RATINGS                  |      |

|     | 4.4.5 General audio adjustment 17   |     | 7.3 OPERATING CONDITIONS                      |      |

|     | 4.4.6 PP volume                     |     |                                               |      |

|     | 4.4.7 PP audio equalization 17      | •   | 7.4 SUPPLY CURRENTS                           |      |

|     | 4.5 PP AUDIO MODES                  |     | 7.6 ANALOG FRONT END                          |      |

|     | 4.5.1 Power management              | )   | 7.7 BATTERY MANAGEMENT                        |      |

|     | 4.5.2 Earpiece mode 20              |     | 7.8 BASEBAND PART                             |      |

|     | 4.5.3 Alert mode 20                 |     | 7.9 RADIO (RF) PART                           |      |

|     | 4.6 CALL HANDLING                   |     | 7.10 RF POWER SUPPLY                          |      |

|     | 4.6.1 FP to PP call 20              |     | 7.11 RF CHANNEL FREQUENCIES                   |      |

|     | 4.6.2 PP to FP call 20              |     | 7.11 RF CHANNEL FREQUENCIES                   | 40   |

|     | 4.6.3 Intercom                      | 0.0 | Design guidelines                             | 47   |

|     | 4.6.4 Conference                    |     | 8.1 APPLICATION SOFTWARE FOR PP               | 47   |

|     | 4.6.5 Page call 20                  |     | 8.2 APPLICATION SOFTWARE FOR FP               | 47   |

|     | 4.7 TONE/MELODY HANDLING            |     | 8.3 HARDWARE DESIGN GUIDELINES                | 47   |

|     | 4.8 DATE AND REAL-TIME CLOCK 20     | )   | 8.3.1 Circuit design guidelines               | 47   |

FINΔI

# **Table of Contents**

|      |      | 8.3.2 PCB Design Guidelines          | 48 |

|------|------|--------------------------------------|----|

|      | 8.4  | MODULE PLACEMENT ON THE MAIN BOAR    | D  |

|      |      |                                      | 49 |

|      | 8.5  | PATTERN FOR PIN 79 ON THE MAIN BOARD | )  |

|      |      |                                      | 49 |

|      | 8.6  | PRECAUTIONS REGARDING UNINTENDED     |    |

|      |      | COUPLING                             | 49 |

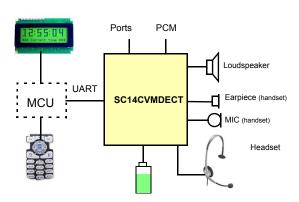

| 9.0  | Exa  | mple application diagram             | 50 |

| 10.0 | ) No | otices to OEM                        | 51 |

|      | 10.  | 1 FCC REQUIREMENTS REGARDING THE EN  | ID |

|      |      | PRODUCT AND THE END USER             | 51 |

|      | 10.2 | 2 INDUSTRY CANADA REQUIREMENTS RE-   |    |

|      |      | GARDING THE END PRODUCT AND THE EN   | ID |

|      |      | USER                                 | 51 |

|      | 10.3 | B END APPLICATION APPROVAL           | 52 |

|      | 10.4 | 4 SAFETY REQUIREMENTS                | 52 |

| 11.0 | ) Pa | ckage information                    | 53 |

|      | 11.1 | SOLDERING PROFILE                    | 53 |

|      | 11.2 | MOISTURE SENSITIVITY LEVEL (MSL)     | 53 |

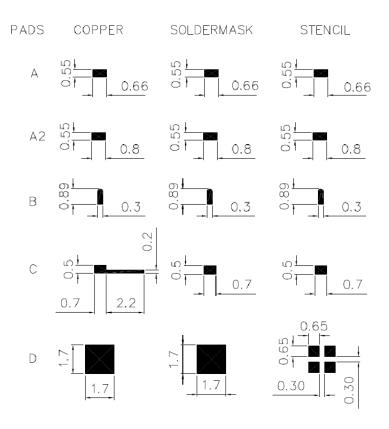

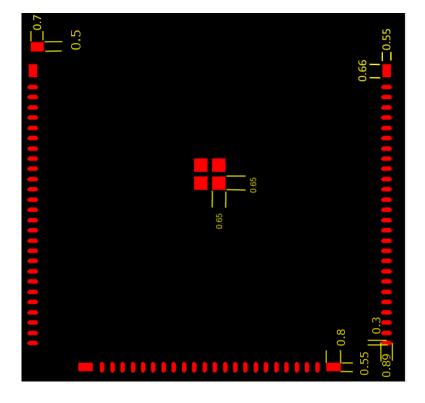

|      | 11.3 | 3 COPPER PAD, SOLDER OPENING AND     |    |

|      |      | STENCIL                              | 54 |

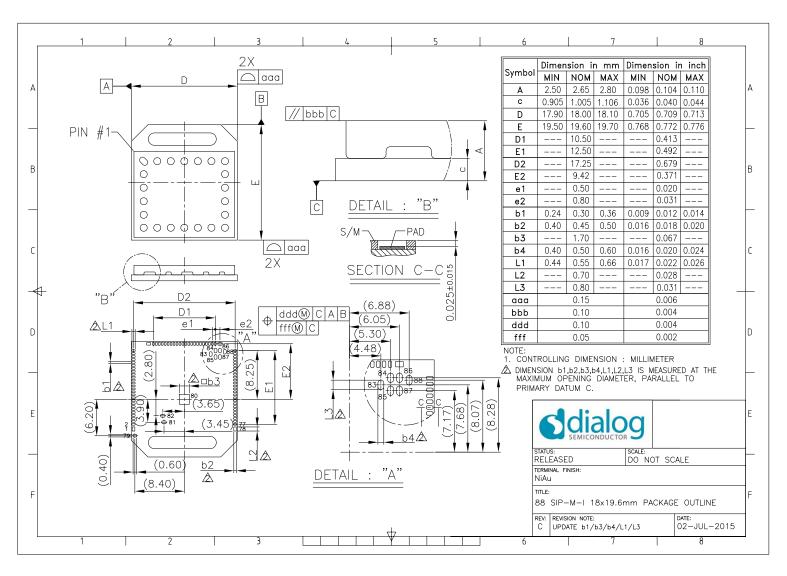

|      | 11.4 | MECHANICAL DIMENSIONS                | 56 |

| 12.0 | ) Re | evision history                      | 57 |

FINAL

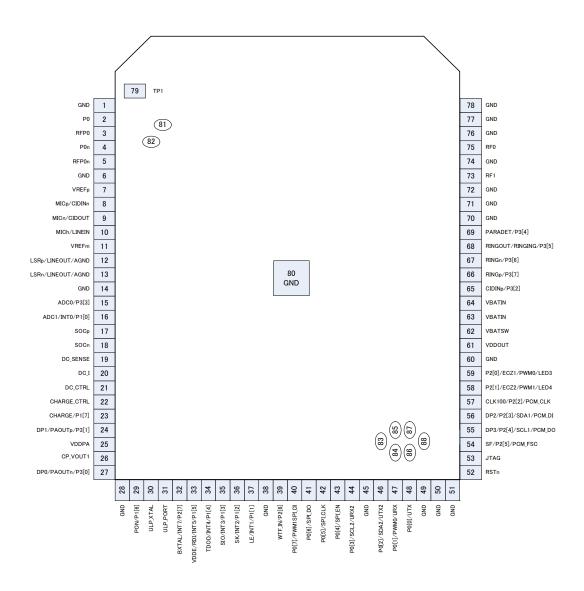

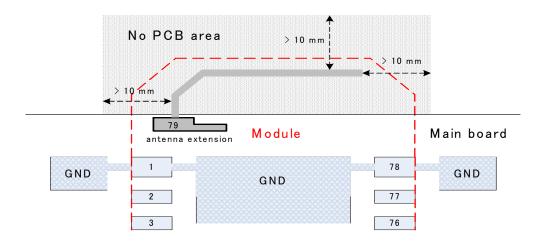

# 1.0 Connection diagram

Figure 1: Connection diagram (top view, leads face down)

**Table 1: Ordering information**

| Part number                | Package | Size (mm) | Shipment form | Pack quantity |

|----------------------------|---------|-----------|---------------|---------------|

| SC14CVMDECT SF01T (Note 2) | MOD88   | 18 x 19.6 | Tray          | 60 (Note 1)   |

| SC14CVMDECT SF02T (Note 3) | MOD88   | 18 x 19.6 | Tray          | 60 (Note 1)   |

**Note 1:** MOQ = 600 pcs.

Note 2: Up to 6 PPs can be registered.

Note 3: Up to 64 PPs can be registered.

FINAL

#### 1.1 PIN DESCRIPTION

#### Table 2: Pin description

| Pin | Module<br>Pin name<br>(Note 4) | In/<br>Out | lout<br>Drive<br>(mA) | Reset<br>State<br>(Note 5)               | Description                                                                                                                                                                                     |  |

|-----|--------------------------------|------------|-----------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | GND                            | -          | -                     | -                                        | Ground                                                                                                                                                                                          |  |

| 2   | P0                             | 0          | 8                     | Hi-Z                                     | Control port for FAD. See 4.13                                                                                                                                                                  |  |

| 3   | RFP0                           | 0          | 8                     | Hi-Z                                     | Control port for FAD. See 4.13                                                                                                                                                                  |  |

| 4   | P0n                            | 0          | 8                     | Hi-Z                                     | Control port for FAD. See 4.13                                                                                                                                                                  |  |

| 5   | RFP0n                          | 0          | 8                     | Hi-Z                                     | Control port for FAD. See 4.13                                                                                                                                                                  |  |

| 6   | GND                            | -          | -                     | -                                        | Ground                                                                                                                                                                                          |  |

| 7   | VREFp                          | 0          | -                     | I                                        | Positive microphone supply voltage                                                                                                                                                              |  |

| 8   | MICp                           | I          | -                     | I                                        | Positive microphone input                                                                                                                                                                       |  |

| 9   | MICn                           | I          | -                     | I                                        | Negative handset microphone input                                                                                                                                                               |  |

| 10  | MICh                           | I          | -                     | I                                        | Headset microphone input with fixed input protection                                                                                                                                            |  |

| 11  | VREFm                          | -          | -                     | -                                        | Negative microphone reference (star point), connect to GND.                                                                                                                                     |  |

| 12  | LSRp                           | 0          | -                     | 0                                        | Positive loudspeaker output                                                                                                                                                                     |  |

| 13  | LSRn                           | 0          | -                     | 0                                        | Negative loudspeaker output                                                                                                                                                                     |  |

| 14  | GND                            | -          | -                     | -                                        | Ground                                                                                                                                                                                          |  |

| 15  | P3[3]                          | Ю          | 8                     | I                                        | I/O Port                                                                                                                                                                                        |  |

| 16  | P1[0]                          | Ю          | 2                     | I-PU                                     | I/O Port                                                                                                                                                                                        |  |

| 17  | SOCp                           | I          | -                     | I                                        | Battery state of charge positive input. Connect to GND if not used. See 4.9                                                                                                                     |  |

| 18  | SOCn                           | I          | -                     | I                                        | Battery state of charge negative input. Star point connected to the SOC resistor. Connect to GND if not used. See 4.9                                                                           |  |

| 19  | DC_SENSE                       | I          |                       | I                                        | Voltage sense input. Connect to GND if not used.                                                                                                                                                |  |

| 20  | DC_I                           | I          |                       | I                                        | Current sense input of DC/DC converter. Connect to GND if not used                                                                                                                              |  |

| 21  | DC_CTRL                        | 0          | 2                     | O-0                                      | Switching clock for the DC/DC converter.                                                                                                                                                        |  |

| 22  | CHARGE_CTRL                    | 0          | 1                     | O-0                                      | Charge control pin. Leave unconnected if not used. See 4.9                                                                                                                                      |  |

| 23  | CHARGE                         | I          | -                     | I-PD<br>(270k<br>fixed<br>pull-<br>down) | Charger connected indication. Switches on the device if voltage > 1.5 V. Must be connected to charger via resistor R > (Vcharger_max-3 V)/10 mA (round to next largest value in range). See 4.9 |  |

| 24  | PAOUTp                         | Ю          | 500                   | O-0 (5k<br>fixed<br>pull-<br>down)       | CLASSD loudspeaker positive outputs                                                                                                                                                             |  |

| 25  | VDDPA                          | I          | -                     | -                                        | CLASSD Audio Amplifier supply voltage up to 3.45 V. GND or leave unconnected if CLASSD Audio Amplifier is not used.                                                                             |  |

| 26  | CP_VOUT1                       | 0          | -                     | I                                        | Charge Pump Output 1. A capacitor of 1 μF to GND is internally connected to this pin.                                                                                                           |  |

| 27  | PAOUTn                         | Ю          | 500                   | O-0 (5k<br>fixed<br>pull-<br>down)       | CLASSD loudspeaker positive output                                                                                                                                                              |  |

| 28  | GND                            | -          | -                     | -                                        | Ground                                                                                                                                                                                          |  |

Table 2: Pin description (Continued)

| Pin | Module<br>Pin name<br>(Note 4) | In/<br>Out | lout<br>Drive<br>(mA) | Reset<br>State<br>(Note 5)         | Description                                                                                                                                                                                                                           |  |

|-----|--------------------------------|------------|-----------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 29  | PON                            | I          | -                     | I (270k<br>fixed<br>pull-<br>down) | Power on, Switches on the device if Voltage > 1.5 V. May be directly connected to VBAT, also with Li-lon batteries. After startup the software takes over then PON pin to keep the device on after which the PON pin may be released. |  |

| 30  | ULP_XTAL                       | I          | -                     | I                                  | 32.768 kHz XTAL clock input. Connect to GND if not used. (Note 6)                                                                                                                                                                     |  |

| 31  | ULP_PORT                       | I          | -                     | I                                  | Ultra Low Power Port Pin. Connect to GND if not used. (Note 6)                                                                                                                                                                        |  |

| 32  | P2[7]                          | Ю          | 8                     | I-PU                               | I/O port                                                                                                                                                                                                                              |  |

| 33  | P1[5]                          | Ю          | 8                     | O-1                                | I/O Port                                                                                                                                                                                                                              |  |

| 34  | P1[4]                          | Ю          | 1/2                   | I-PD                               | I/O port                                                                                                                                                                                                                              |  |

| 35  | P1[3]                          | Ю          | 1/2                   | I-PD                               | I/O Port                                                                                                                                                                                                                              |  |

| 36  | P1[2]                          | Ю          | 2                     | I-PD                               | I/O Port                                                                                                                                                                                                                              |  |

| 37  | P1[1]                          | Ю          | 2                     | I-PU                               | I/O Port                                                                                                                                                                                                                              |  |

| 38  | GND                            | -          | -                     | -                                  | Ground                                                                                                                                                                                                                                |  |

| 39  | P2[6]                          | Ю          | 2                     | I-PU                               | I/O port                                                                                                                                                                                                                              |  |

| 40  | P0[7] / SPI_DI                 | Ю          | 8                     | I-PU                               | I/O Port<br>SPI Data Input                                                                                                                                                                                                            |  |

| 41  | P0[6] / SPI_DO                 | Ю          | 8                     | I-PU                               | I/O Port<br>SPI Data Out                                                                                                                                                                                                              |  |

| 42  | P0[5] / SPI_CLK                | Ю          | 8                     | I-PU                               | I/O Port<br>SPI Clock                                                                                                                                                                                                                 |  |

| 43  | P0[4] / SPI_EN                 | Ю          | 8                     | I-PU                               | I/O port SPI_EN: Active low.                                                                                                                                                                                                          |  |

| 44  | P0[3] / SCL2 /<br>URX2         | Ю          | 8                     | I-PU                               | I/O port Access bus clock, UART Serial In.                                                                                                                                                                                            |  |

| 45  | GND                            | -          | -                     | -                                  | Ground                                                                                                                                                                                                                                |  |

| 46  | P0[2] / SDA2 /<br>UTX2         | Ю          | 8                     | I-PU                               | I/O port<br>Access bus data, UART Serial Out.                                                                                                                                                                                         |  |

| 47  | P0[1] / URX                    | Ю          | 8                     | I-PD<br>(10k)                      | I/O port<br>UART Serial In                                                                                                                                                                                                            |  |

| 48  | P0[0] / UTX                    | 0          | 8                     | I-PU                               | I/O Port<br>UART Serial Out                                                                                                                                                                                                           |  |

| 49  | GND                            | -          | -                     | -                                  | Ground                                                                                                                                                                                                                                |  |

| 50  | GND                            | -          | -                     | -                                  | Ground                                                                                                                                                                                                                                |  |

| 51  | GND                            | -          | -                     | -                                  | Ground                                                                                                                                                                                                                                |  |

| 52  | RSTn                           | I          | 1                     | I-PU<br>(200k)                     | Active low Reset input with Schmitt-trigger input, open-drain output. Input may not exceed 2.0 V. An internal capacitor of 47 nF is mounted on this pin.                                                                              |  |

| 53  | JTAG                           | Ю          | 8                     | I-PU<br>(1k)                       | JTAG-SDI+; one wire Debug interface with open-drain.                                                                                                                                                                                  |  |

| 54  | P2[5]/PCM_FSC                  | Ю          | 8                     | I-PU                               | I/O Port PCM_FSC: PCM Frame Sync                                                                                                                                                                                                      |  |

| 55  | P2[4]/SCL1/<br>PCM_DO          | Ю          | 8                     | I-PU                               | I/O port SCL1; I2C clock PCM_DO: PCM Data output                                                                                                                                                                                      |  |

FINΔI

Table 2: Pin description (Continued)

| Pin   | Module<br>Pin name<br>(Note 4) | In/<br>Out | lout<br>Drive<br>(mA) | Reset<br>State<br>(Note 5) | Description                                                                     |  |

|-------|--------------------------------|------------|-----------------------|----------------------------|---------------------------------------------------------------------------------|--|

| 56    | P2[3]/SDA1 /<br>PCM_DI         | Ю          | 8                     | I-PU                       | I/O Port<br>SDA1: I2C Data<br>PCM_DI: PCM Data input                            |  |

| 57    | P2[2]/PCM_CLK                  | I/O        | 8                     | I-PD                       | I/O Port PCM_CLK: PCM clock input/output                                        |  |

| 58    | P2[1] / PWM1 /<br>LED4         | Ю          | 8                     | I                          | I/O Port PWM1: Pulse Width Modulation output LED4: 2.5 mA/5 mA LED current sink |  |

| 59    | P2[0]/ PWM0 /<br>LED3          | Ю          | 8                     | I                          | I/O Port<br>PWM0: -<br>LED3: 2.5 mA/5 mA LED current sink                       |  |

| 60    | GND                            | -          | -                     | -                          | Ground                                                                          |  |

| 61    | VDDOUT                         | -          | -                     | -                          | Test purpose only. Must be left unconnected.                                    |  |

| 62    | VBATSW                         |            |                       |                            | Test purpose only. Must be left unconnected.                                    |  |

| 63    | VBATIN                         | I          | -                     | -                          | Main supply voltage < 3.45 V.                                                   |  |

| 64    | VBATIN                         | I          | -                     | -                          | Main supply voltage < 3.45 V.                                                   |  |

| 65    | P3[2]                          | Ю          | 8                     | I                          | I/O Port                                                                        |  |

| 66    | P3[7]                          | Ю          | 4                     | I                          | I/O Port                                                                        |  |

| 67    | P3[6]                          | Ю          | 4                     | 1                          | I/O Port                                                                        |  |

| 68    | P3[5]                          | Ю          | 4                     | I                          | I/O Port                                                                        |  |

| 69    | P3[4]                          | Ю          | 8                     | I                          | I/O Port                                                                        |  |

| 70    | GND                            | -          | -                     | -                          | Ground                                                                          |  |

| 71    | GND                            | -          | -                     | -                          | Ground                                                                          |  |

| 72    | GND                            | -          | -                     | -                          | Ground                                                                          |  |

| 73    | RF1                            | -          | -                     | -                          | RF signal for external antenna. See 4.13                                        |  |

| 74    | GND                            | -          | -                     | -                          | Ground                                                                          |  |

| 75    | RF0                            | -          | ı                     | -                          | RF signal for external antenna. See 4.13                                        |  |

| 76    | GND                            | -          | -                     | -                          | Ground                                                                          |  |

| 77    | GND                            | -          | -                     | -                          | Ground                                                                          |  |

| 78    | GND                            | -          | ı                     | -                          | Ground                                                                          |  |

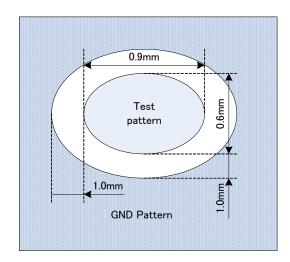

| 79    | TP1                            | -          | -                     | -                          | Tuning point for internal antenna. Follow instructions of Section 8.5.          |  |

| 80    | GND                            | _          | -                     | -                          | Ground                                                                          |  |

| 81-88 | TP2 to TP9                     | NC         |                       |                            | Must be left unconnected. See section 8.3.2 and Figure 36.                      |  |

Note 4: "NC" means: leave unconnected.

"GND" means internally connected to the module ground plane. Every GND pin should be connected to the main PCB.ground plane.

Note 5: All digital inputs have Schmitt trigger inputs. After reset all I/Os are set to input and all pull-up or pull-down resistors are enabled unless otherwise specified.

PU = Pull-up resistor enabled, PD = Pull-down resistor enabled, I = input,

O = output, Hi-Z = high impedance, 1 = logic HIGH level, 0 = logic LOW level

Refer also to Px\_DIR\_REGs for INPUT/OUTPUT and Pull-up/Pull-down configurations

Note 6: All ULP pins use snap-back devices as ESD protection, which (when triggered) have a holding voltage below the typical battery voltage.

This means that the snap-back device of a ULP pin may remain conductive, when triggered while the pin is directly connected to the battery voltage. If any of the ULP pins are directly or indirectly electrically accessible on the outside of the application, system level ESD precautions must be taken to ensure that the snap-back device is not triggered while in active mode, to prevent the chip from being damaged.

# Cordless Voice Module FINAL

#### 2.0 Introduction

#### 2.1 SCOPE

The SC14CVMDECT SF is a programmable DECT module for voice and data services. The internal software stack receives commands and data from the application, for instance to set up a link to other modules. The application software can be implemented on the module itself or on an external host processor. The internal FLASH provides user space where custom applications can be located.

The module converts analog signals to a digital stream, compresses/decompresses them according to the DECT standards and transmits/receives them over the air interface. The DECT protocol stack in each module supports both PP and FP functionality.

The embedded software running on the internal microcontroller (CR16) supports all protocol layers up to the network layer. The module can be controlled by software running on the internal controller as well as from an external controller via the UART.

#### 2.2 REFERENCES

- 1. CVM FP API Documentation package.

- 2. CVM PP API Documentation package.

- Athena Eclipse User Manual, v1.02, Dialog Semiconductor, Cordless Software and Tools.

- SC14CVMDECT EEPROM (VES) map for PP (NatalieV3PpCvm Eeprom\_vXXXX.html).

- AN-D-174, SC14480 Battery Management; using the State of Charge function, Application Note, Dialog Semiconductor.

- AN-D-212, SC14CVMDECT\_SFxx\_DB External Antenna Design and Leveraging Modular Approval, Application Note, Dialog Semiconductor.

- 7. AN-D-222, SC14CVMDECT production pairing, Application Note, Dialog Semiconductor.

#### 2.3 GLOSSARY AND DEFINITIONS

| AFE          | Analog Front End                                      | 11211         | • |

|--------------|-------------------------------------------------------|---------------|---|

| API          | Application Programming Interface                     | RSSI          | F |

| Baby monitor | Same as intercom but optionally voice activated       | Sidetone      | F |

| CAT-iq       | Cordless Advanced Technology,<br>Internet and Quality | SLR           | S |

| CODEC        | COder and DECoder                                     | SPI           | S |

| CoLA         | Co-Located Application                                | UART          | L |

| Conference   | Same as intercom, but including an external party     | ULE           | ι |

| CRC          | Cyclic Redundancy Check                               | VAD           | ٧ |

| CVM          | Cordless Voice Module                                 | VES           | ٧ |

| DECT         | Digital Enhanced Cordless Telephone                   | Walkie Talkie | C |

|              |                                                       |               |   |

| DSP | Digital Signal Processor |

|-----|--------------------------|

EMC Equipment Manufacturer's Code

ESD ElectroStatic Discharge FAD Fast Antenna Diversity

FP Fixed Part

GAP Generic Access Profile (DECT)

GFSK Gaussian Frequency Shift Keying

HPM High Power Mode

Inband tones Tones played by the application itself

and not from external e.g. line.

Intercom Internal call between FP and PP(s)

IPEI International Portable Equipment

Identity (ETSI EN 300 175-6)

IWU InterWorking Unit (ETSI EN 300 175-

1)

LCD Liquid Crystal Display

LDO Low Drop Out (regulator)

LDR Low Data Rate

LPM Low Power Mode

MCU Micro Controller Unit

MMI Man Machine Interface (keypad, LCD,

buzzer, microphone, earpiece, etc.)

NTP Normal Transmitted Power

PAEC Perceptual Acoustic Echo Canceller

PC Personal Computer, IBM compatible

PCB Printed Circuit Board

PP Portable Part

PSTN Public Switched Telephone Network

RF Radio Frequency

RFPI Radio Fixed Part Identity (ETSI EN

300 175-6)

RLR Receive Loudness Rating

RSSI Radio Signal Strength Indication (ETSI

EN 300 175-1)

Sidetone Feedback of microphone signal to

earpiece

SLR Sending Loudness Rating

PI Serial Peripheral Interface Bus

UART Universal Asynchronous Receiver and

Transmitter

ULE Ultra Low Energy

VAD Voice Activity Detection

VES Virtual EEPROM Storage

Walkie Talkie Call between two PPs without an FP

Cordless Voice Module FINAL

#### 3.0 Cordless Voice Module functions

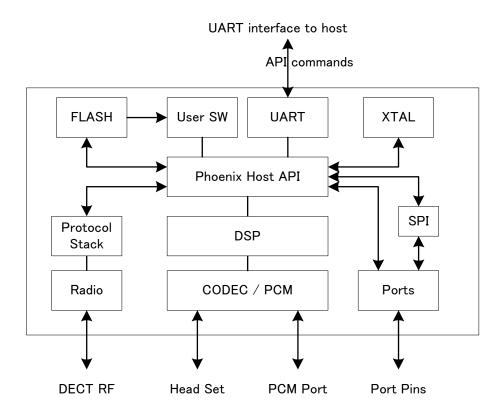

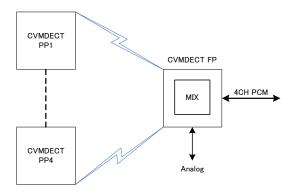

This section describes the key functions and features supported by the SC14CVMDECT SF as shown in Figure 2.

Figure 2: SC14CVMDECT SF functional overview

#### 3.1 MODULE HARDWARE

The SC14CVMDECT SF internal hardware consists of:

- An internal microprocessor is running from FLASH and handles the API call coming from UART or embedded user software.

- A 4 kB VES (Virtual EEPROM Storage) used by the protocol stack and for user variables.

- A DSP for the audio signal processing like ADPCM voice compression towards the CODEC.

- A CODEC converts the analog signals to digital signals and vise versa.

- Input/Output ports which can be toggled high/low as an output or a high/low digital level can be read as an input.

- A 20.736 MHz XTAL. This crystal is automatically tuned by the PP module software for optimal radio performance.

- Voltage regulators convert the external supply voltage (VBAT) to stable supply voltages for the core and the I/Os.

- A DECT radio transceiver with a built-in antenna cir-

cuit. The antenna itself is integrated into the module, relieving the product designer from RF expertise.

A full duplex UART for communication with an optional host processor.

#### 3.2 SOFTWARE CONTROL

The application software is written by the customer and has to manage the call control and also the MMI functions. The supported API software includes the Network layer that is defined in figure 1 of the EN300 175-3 document, which describes the DECT protocol stack. Detailed functions and data flows, including some example sequences, can be found in document reference [1] for FP and [2] for PP.

The default configuration of the SC14CVMDECT SF module software is: US DECT, FP and CoLA enabled.

#### 3.3 DECT PROTOCOL STACK

The SC14CVMDECT SF internal protocol stack is based on the ETSI DECT specifications and is compliant with ETSI 300 444 (GAP).

The product supports up to 6 DECT GAP compliant PP units to one FP station.

FINΔI

#### 3.4 PORTABLE PART CONFIGURATION

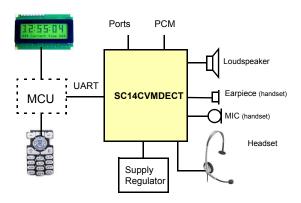

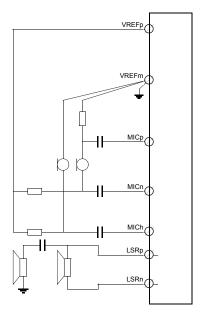

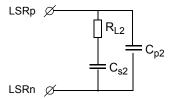

A Portable Part configuration with SC14CVMDECT SF requires additional external parts as shown in Figure 3.

Figure 3: PP configuration

Table 3 provides an overview of the supported interfaces for a portable part.

Table 3: PP support overview

| Item                               | Supported | Remark                                                                                    |

|------------------------------------|-----------|-------------------------------------------------------------------------------------------|

| Battery management                 | Yes       | Supported by API                                                                          |

| Keypad                             | No        | On external MCU                                                                           |

| Display                            | No        | On external MCU                                                                           |

| I/O Ports                          | Yes       | All digital I/O port pins can be controlled by API                                        |

| PCM interface                      | Yes       | 1x 16 bits serial I/O, PCM_FSC 8 kHz/16 kHz                                               |

| UART                               | Yes       | 115.2 kbit/s, used for API-commands                                                       |

| Headset detection                  | Yes       | Supported by API                                                                          |

| LSR (Earpiece, headset)            | Yes       | Connected to LSRp and/or LSRn supports single-end and differential (Note 7)               |

| MIC (Earpiece, headset, handsfree) | Yes       | Connected to MICp and/or MICn and/or MICh supports single-ended and differential (Note 7) |

| Handsfree speaker                  | Yes       | Connected to PAOUTp/n (Note 7)                                                            |

| Radio                              | Yes       | Integrated single antenna and support for external antenna(s)                             |

Note 7: AFE setting is configurable, refer to document [2].

FINΔI

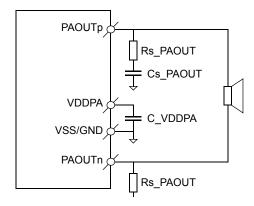

#### 3.5 FIXED PART CONFIGURATION

A Fixed Part configuration with SC14CVMDECT SF requires additional external parts as shown in Figure 4.

Figure 4: FP configuration

Table 4 provides the overview of required and available interfaces for a basic or a feature rich cordless FP with the SC14CVMDECT SF.

Table 4: FP support overview

| Item                               | Supported | Remark                                                                                  |

|------------------------------------|-----------|-----------------------------------------------------------------------------------------|

| Supply Regulator                   | No        | Use external 3.3 V LDO                                                                  |

| Keypad                             | No        | On external MCU                                                                         |

| Display                            | No        | On external MCU                                                                         |

| I/O Ports                          | Yes       | All digital I/O port pins can be controlled via API                                     |

| PCM interface                      | Yes       | 4x 16 bits serial I/O, PCM_FSC 8 kHz/16 kHz                                             |

| UART                               | Yes       | 115.2 kbit/s, used for API-commands                                                     |

| Headset detection                  | No        | Not supported by API                                                                    |

| LSR (Earpiece, headset)            | Yes       | Connected to LSRp and/or LSRn supports single-end and differential (Note 8)             |

| MIC (Earpiece, headset, handsfree) | Yes       | Connected to MICp and/or MICn and/or MICh supports single-end and differential (Note 8) |

| Handsfree speaker                  | Yes       | Connected to PAOUTp/n (Note 8)                                                          |

| PSTN Line interface                | No        | Not supported by API                                                                    |

| Radio                              | Yes       | Integrated single antenna and support for external antenna(s)                           |

Note 8: AFE setting is configurable, refer to document [1].

FINAL

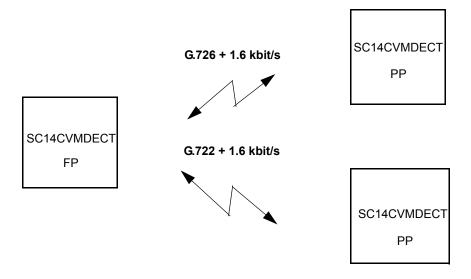

#### 3.6 VOICE COMMUNICATION

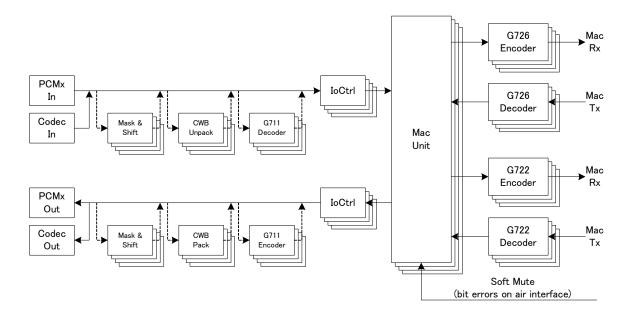

An FP supports up to 64 registered PPs, where 4 of these PPs can be in a call at the same time. Multiple simultaneous calls are supported. Supported voice codec is G.726 (32 kbit/s ADPCM) and G.722 (64 kbit/s ADPCM). See Figure 5.

#### 3.7 LIGHT DATA APPLICATION

The SC14CVMDECT SF supports Low Data Rate (LDR) transmission up to 1.6 kbit/s with IWU to IWU messaging. The LDR can be used in combination with voice communication. See Figure 5.

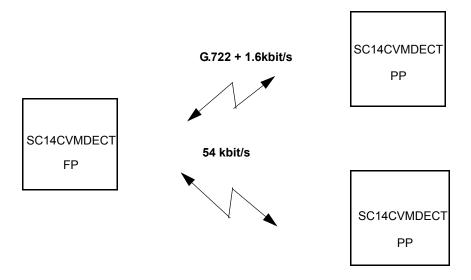

#### 3.8 LU10 DATA APPLICATION

The SC14CVMDECT SF supports CAT-iq LU10 data transmission up to 54 kbit/s. Since LU10 data communication uses the B-Field it cannot be used in combination with voice communication. See Figure 6.

Figure 5: Voice and LDR data communication

Figure 6: LU10 data application

**FINAL**

#### 3.9 GENERAL FEATURES

#### Table 5: Supported general features

| Functionality (Note 9)          | PP<br>support | FP<br>support | Remark                                                                                                      |

|---------------------------------|---------------|---------------|-------------------------------------------------------------------------------------------------------------|

| Call handling                   |               |               |                                                                                                             |

| Conferencing                    | -             | Yes           | Call between FP and 4x PP                                                                                   |

| Intercom                        | Yes           | Yes           | Call between FP and 4x PP                                                                                   |

| Walkie Talkie mode              | Yes           | -             | Call between PP and PP without FP                                                                           |

| Baby monitor                    | Yes           | -             | Voice Activated PP. See document reference [2]                                                              |

| Voice over PCM interface        | Yes           | Yes           | μ-law (64 kbit/s), A-law (64 kbit/s), G.726 ADPCM (32 kbit/s), G.722 ADPCM (64 kbit/s), Linear (128 kbit/s) |

| Call transfer                   | Yes           | Yes           | Transfer call between PPs on FP                                                                             |

| Page call                       | Yes           | Yes           | FP pages all PPs (PP locator)                                                                               |

| Protocol                        | •             | •             |                                                                                                             |

| Manual registration             | Yes           | Yes           |                                                                                                             |

| Wire registration               | Yes           | Yes           | See document reference [7]                                                                                  |

| Number of CVM PP registrations  | -             | Yes           | 1 to 6 for SF01                                                                                             |

| per FP                          |               |               | 1 to 64 for SF02 (Note 10)                                                                                  |

| Number of ULE PP registrations  | -             | Yes           | 1 to 180 for SF01                                                                                           |

| per FP                          |               |               | 1 to 64 for SF02 (Note 10)                                                                                  |

| Audio and tone                  | •             | •             |                                                                                                             |

| Microphone mute                 | Yes           | Yes           |                                                                                                             |

| Tone generation                 | Yes           | No            | Melody generator with 7 polyphonic tones                                                                    |

| Audio Volume control            | Yes           | Yes           |                                                                                                             |

| Tone Volume control             | Yes           | No            |                                                                                                             |

| Headset support                 | Yes           | Yes           |                                                                                                             |

| Handsfree/Speakerphone          | Yes           | No            |                                                                                                             |

| General                         | •             | •             |                                                                                                             |

| Real time clock                 | Yes           | Yes           | Accuracy depending directly on crystal                                                                      |

| Real time clock synchronization | Yes           | Yes           | All PP clocks are kept in synchronization with the FP                                                       |

| SW EEPROM (VES) Storage         | Yes           | Yes           | Internal on module                                                                                          |

| Battery Charge Management       | Yes           | No            |                                                                                                             |

| PSTN line interface support     | -             | No            | PSTN software on request                                                                                    |

| I/O port support                | Yes           | Yes           |                                                                                                             |

| Port Interrupt support          | No            | No            |                                                                                                             |

| Automatic headset detection     | Yes           | No            |                                                                                                             |

| Low speed data                  | Yes           | Yes           | 1.6 kbit/s                                                                                                  |

| LU10 data channel               | Yes           | Yes           | 54 kbit/s (Note 11)                                                                                         |

| CAT-iq up to version 2.0, 3.0   | Yes           | Yes           |                                                                                                             |

Note 9: These features can be supported by combined API commands in user software.

$\textbf{Note 10:} \ \ \textbf{The number of PP registrations includes both CVMDECT PP and ULE PP devices}.$

Note 11: SF02 supports one channel LU10 simultaneously.

FINΔI

# 4.0 Functional description

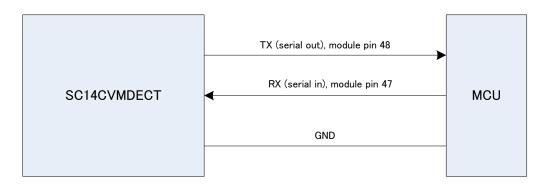

#### **4.1 UART INTERFACE**

The UART is normally used for API commands, but can also be used for software upgrades and debugging.

The UART is a full duplex UART with frame type:

- 1 start bit,

- 8 data bits (LSB first),

- 1 stop bit,

- no parity,

- up to 115.2 kBd.

The UART hardware interface uses only TX/RX (see Figure 7).

Figure 7: UART hardware configuration

**Caution:** All UART signals are 1.8 V, input max. 3.45 V (see Table 18, Table 21 and Table 22). An external V.24 line driver must be provided if the UART port of the module is connected to a standard V.24 device (±12 V). Connecting the module without a driver may damage the module.

#### **4.2 VES (VIRTUAL EEPROM STORAGE)**

#### 4.2.1 VES layout

The SC14CVMDECT SF PP and FP include a 4 kB VES which is divided into two areas (see Table 6).

Table 6: VES map

| VES space         | Size   | Usage                                                          |

|-------------------|--------|----------------------------------------------------------------|

| SC14CVMDECT<br>SF | 3.6 kB | Used for RF, audio,<br>battery, tone setup,<br>data base, etc. |

| User              | 0.4 kB | Can be used for MMI applications such as User information.     |

VES is supported as virtual EEPROM with the internal FLASH.

A detailed overview of the VES parameters can be found in document reference [4].

Some parts of the VES parameters are read into the SC14CVMDECT SF during the start up and other parts

are used by the SC14CVMDECT SF software during execution.

The VES parameters are divided into two types:

- Factory type

- Normal type

The "factory" type is specific for the SC14CVMDECT SF and should only be set by production. The "factory" type parameters are either adjustments used by the baseband or the radio interface, or are used to set up the SC14CVMDECT SF into special modes. The "factory" type parameters will only be modified by changing the factory programmed default value. See document reference [4].

The "normal" VES parameters can be reset to their default values via software.

#### 4.2.2 VES access by MCU

The host is able to read or modify the VES parameters or limited free VES areas via API command.

# dialog

#### **Cordless Voice Module**

FINAL

#### 4.3 AUDIO CONFIGURATIONS

The SC14CVMDECT SF audio supports standard DECT audio qualities. The audio gain and volume parameters are placed in the VES. The DECT gains can be adjusted to meet the TBR38 and TBR10 audio level requirements by using the SC14CVMDECT SF application reference design. For other line and acoustic designs it is required to adjust and tune the audio setup.

#### 4.3.1 Audio connection

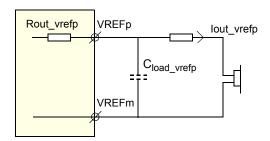

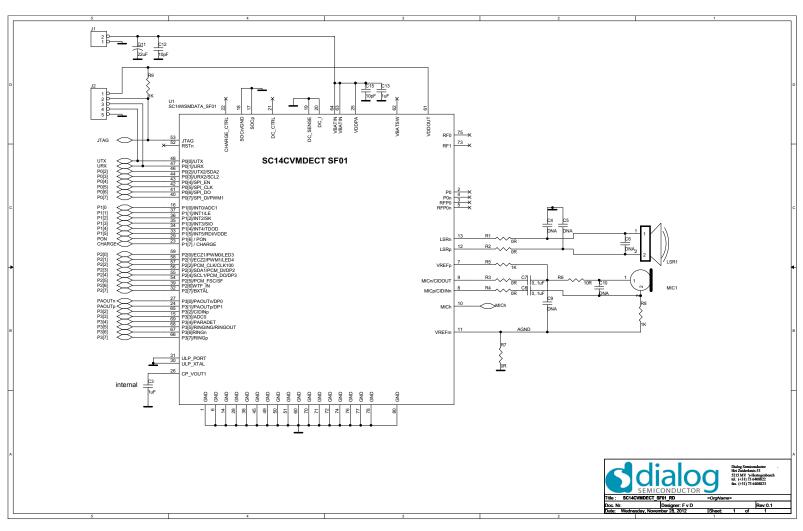

The SC14CVMDECT SF PP audio connections are shown in Figure 8. Refer to "Example application diagram" on page 49 for detailed component values.

Figure 8: Audio connections

## Earpiece or small loudspeaker connection

The earpiece loudspeaker can be connected either differentially or single-ended. Dynamic loudspeakers with an impedance of 30  $\Omega$  can be connected, as well as ceramic loudspeakers equivalent to 600  $\Omega$  and 30  $\mu\text{F}.$  Refer to Table 28 for a detailed specification or the earpiece loudspeakers.

The earpiece is connected to the LSRp and LSRn pins.

### Microphone connection

The microphone can be connected either single-ended via MICp or differentially to MICp and MICn.

#### **Headset connection**

The headset microphone must be connected to the MICh pin. The headset earpiece is connected to the LSRp.

#### Microphone supply connection

For active microphones a voltage source with high supply voltage rejection ratio is provided on supply pins VREFp/VREFm. Filtering of internal and external reference voltages is provided by an internal capacitor. No external capacitor shall be connected to pin VREFp. To avoid audible switching noise it is important that the ground supply signals are directly "star point" connected to the VREFm and not via a common ground plane. From this VREFm star point, one connection is made to the common ground plane.

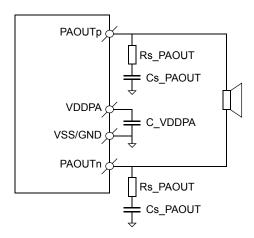

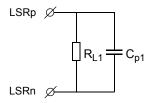

#### Loudspeaker connection

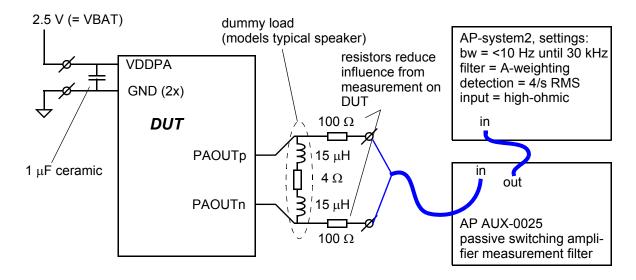

For the handsfree operation a 4  $\Omega$  loudspeaker must be connected to the PAOUTp and PAOUTn pins as shown in Figure 9. The VDDPA is the supply pin.

Figure 9: Loudspeaker connection

Refer to Table 31 for a detailed specification of the external components around the loudspeaker. These components are necessary to guarantee the lifetime of the module.

# dialog

#### **Cordless Voice Module**

FINAL

#### 4.4 AUDIO ROUTING

Figure 10: FP audio routing

#### 4.4.1 FP audio routing

Figure 10 shows the audio routing for an FP. Input and output signals are supported both for the internal codec and the PCM, and the Air interface supports G.726 (32 kbit/s ADPCM) and G.722 (64 kbit/s ADPCM). The internal software supports up to 4 audio channels simultaneously. Supported sample rates are 8 kHz and 16 kHz.

FP does not support acoustic or line echo cancellation.

#### 4.4.2 FP audio level adjustment

The internal codec audio levels can be controlled with the parameters MicGain and LsrGain.

The MicGain range is 0 to 30 dB in steps of 2 dB and a value of -128 will mute the input signal, default is 0 dB.

The LsrGain range is +2 dB to -12 dB in steps of 2 dB, default is +2 dB. See document reference[1].

#### 4.4.3 PP audio routing

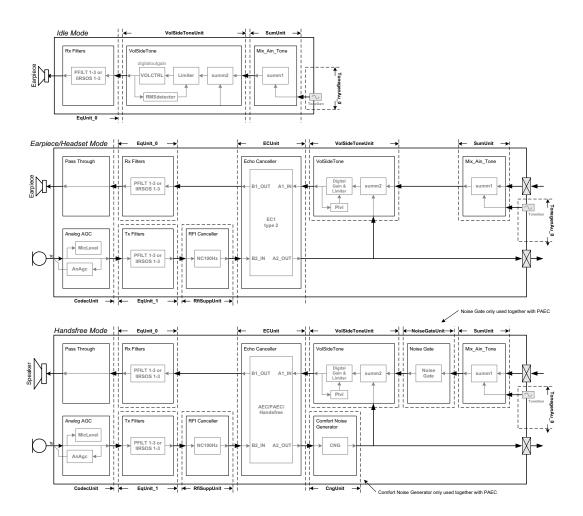

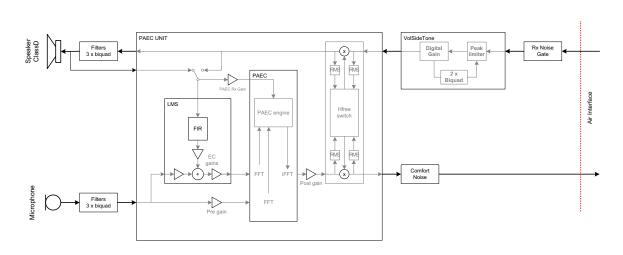

Figure 11 and Figure 12 show the different audio routing modes of a PP. Figure 11 shows an overall audio routing and Figure 12 shows the detailed audio routing for the speakerphone of PP (FP does not support speakerphone).

#### 4.4.4 PP audio codec adjustment

The audio codec settings for the loudspeaker and microphone must be pre-configured in the VES for each mode. The VES parameter fields for

Audio.Earp.xxx Audio.Heads.xxx

#### Audio.SpkPh.xxx

have a default value and maybe fine-tuned for the application. See document reference [4].

#### 4.4.5 General audio adjustment

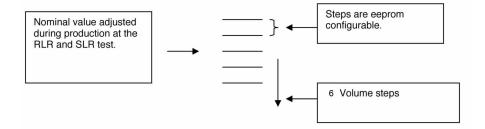

For each audio mode, the receive (RLR) and transmit (SLR) audio paths must be adjusted. RLR and SLR are adjusted in the registers in the VES for each audio state; see document reference [4]. Figure 13 shows this image.

#### 4.4.6 PP volume

The PP supports 6 volume steps, which are VES configurable through parameter fields Audio.Earp.Vol.xxx, the Audio.Heads.Vol.xxx and Audio.SpkPh.Vol.xxx. The volume steps must be set initially in the VES during production; see document reference [4].

#### 4.4.7 PP audio equalization

To enable adjustments of the frequency response the PP contains four programmable filters: 2 in RX direction and 2 in TX direction (see Figure 11).

By default these filters are loaded with bypass coefficients. These can be modified by loading new coefficients via API commands.

Equalizer filters are part of the audio routes for all audio modes and are placed as shown in Figure 11.

For a detailed description of the filter functionality refer to the API documentation; see document reference [2].

FINΔI

Figure 11: PP audio routing

Figure 12: Extended speakerphone for PP

Figure 13: Handset volume configuration

#### 4.5 PP AUDIO MODES

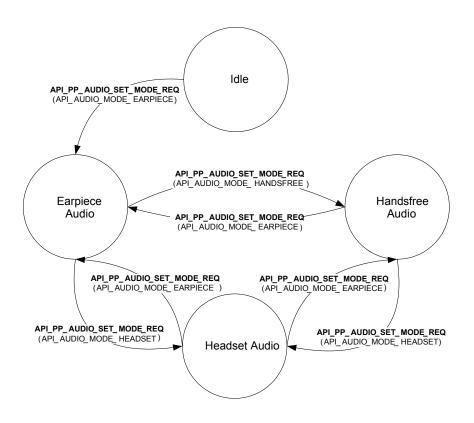

The PP audio handling consists of four audio states (see Figure 14). In these states the audio subsystem is configured for a certain audio mode:

- 1. Idle mode (not relevant for microphone configuration)

- 2. Earpiece mode (Handset speaker)

- 3. Handsfree or Speakerphone mode

#### 4. Headset mode

Selection between the modes is done via API calls; see document reference [2].

The Alert state is for tone playing and is entered automatically when tones are played using the API calls. The Alert state can originate from idle, earpiece, handsfree or headset mode.

Figure 14: PP audio modes

#### 4.5.1 Power management

To minimize the current consumption the PP will shut down all codec amplifiers in Idle mode. This means that all reference voltages in the analog front-end will

be disabled. This feature can be disabled in the VES if the reference voltages for some reasons are needed in Idle mode.

# **dialog**SEMICONDUCTOR

# **Cordless Voice Module**

FINΔI

#### 4.5.2 Earpiece mode

In Earpiece mode (Handset speaker) an artificial sidetone is generated. The level of the sidetone can be adjusted and setup in the VES through parameter fields Audio.Earp.Vol.Elementx, SideToneGain and Audio.Heads. Elementx.SideToneGain. In Earpiece mode it is possible to adjust the volume in the Earpiece via API calls. In Earpiece mode the PP audio is routed as shown in Figure 11.

#### 4.5.3 Alert mode

The Alert mode is for generating tones and melodies on the Speakerphone loudspeaker. In Alert mode it is possible to adjust the volume in the speaker via API calls. Inband tones will be affected by the volume adjustments, since the volume control takes place after tones are added to the signal. Figure 11 shows the Audio flow.

#### 4.6 CALL HANDLING

#### 4.6.1 FP to PP call

When the FP initializes a call to a PP, a radio connection is set up to all PP applications to make it possible for the PP application software to indicate that there is an incoming call.

It is possible to configure the ringing indication using broadcast to make all 64 PPs ringing.

#### 4.6.2 PP to FP call

When the MMI software signals the PP to establish a call, the PP opens the radio connection to the FP.

#### 4.6.3 Intercom

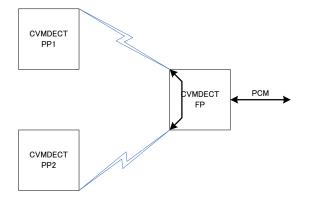

Figure 15 shows the audio routing of an internal call between PP1 and PP2. In the FP no transcoding takes place.

Figure 15: Intercom connection

#### 4.6.4 Conference

Figure 16 shows the audio routing of a 9-party conference call.

Figure 16: Conference connection

#### 4.6.5 Page call

The Page call is an FP functionality used to locate the registered PPs. FP paging does not establish a normal audio connection and is terminated when answered by the PP

#### 4.7 TONE/MELODY HANDLING

The tone component handles the generation of various tones in the device. Both tones/melodies in a PP configuration are supported.

The main features of the tone component are:

- Ringer tones and melodies (7-tone polyphonic)

- Alert tones (key sound, error tones, confirmation tones, etc.)

- Inband tones (dial tone, net-congestion tone, busy tone, etc.)

- · Single tone generation

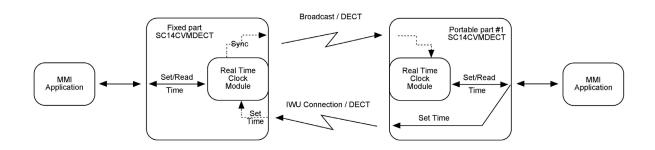

#### 4.8 DATE AND REAL-TIME CLOCK

The FP has a real-time clock feature, which (when activated) broadcasts the date and time of day to the PPs. Activation of the date and real-time clock is done by setting the date and time via the PP.

The clock supports hours, minutes and date. The date supports leap years. Daylight saving time is not supported and must be handled by the MMI application.

The PP clock is synchronized with the FP every time a broadcast is received. If the PP goes out-of-lock, the PP itself calculates the clock time until the PP is again within the range of the FP. The updated clock time can be read locally via the MMI software.

To adjust the clock in the FP, a service connection can be set up via commands from the PP.

The clock can also be read and set directly from an external microprocessor or through the MMI software on the FP.

The real-time clock accuracy depends directly on the SC14CVMDECT SF crystal.

When the SC14CVMDECT SF is configured as a PP, the clock has the same accuracy as the FP clock.

When the PP synchronises with an FP, the PP crystal is synchronized with the FP crystal and the PP clock will change accordingly.

The accuracy is expected to be within 1 minute for up to 6 weeks without being locked to an FP.

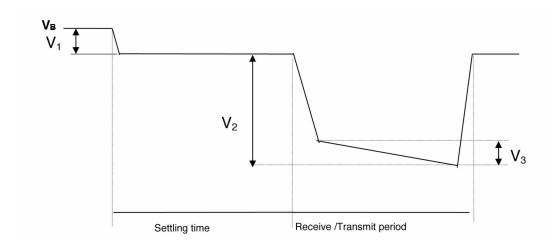

Figure 17: Clock synchronization

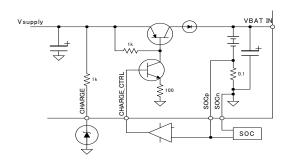

#### **4.9 BATTERY MANAGEMENT**

Figure 18: Handset (PP) application with 2x NiMH

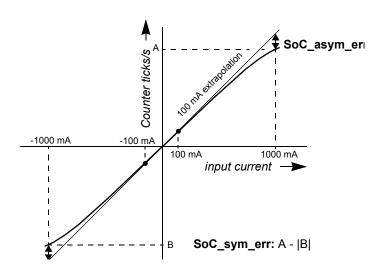

Figure 18 shows a handset application with NiMH. SOC (State Of Charge) is used to measure the amount of charge in the rechargeable batteries.

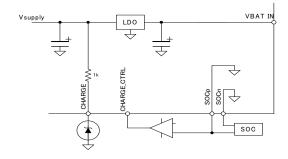

Figure 19 shows an FP application. The FP uses an external LDO, so the SOC pins are not used and can be connected to GND.

The PP API supports battery management to calculate the battery capacity and to indicate charge status. Refer to API document [2].

The SOC circuit is used to very accurately determine the amount of charge in rechargeable batteries as well as the discharge state of Alkaline batteries. This information is essential for the battery charging algorithm and necessary for battery status indication to the user. Battery status information is supported by the API. Detailed information can be found in AN-D-174 (Battery Management) [5].

Figure 19: Base station (FP) application

Pin CHARGE\_CTRL is driven high when either the "sensed voltage on the VBAT pin" is lower than the voltage setting or "sensed current via SOCp" is lower than the current setting. Pin CHARGE\_CTRL can drive up to 500  $\mu\text{A}$  as source current (see Table 32). Detailed setting information can be found in document [4] under "Battery settings".

#### 4.10 PROTOCOL STACK

The protocol stack handles the RF interface, the MAC-, DLC-, NWK-layer and encryption according to the DECT standard EN300 175 1-9.

# 4.10.1 DECT TBR22

The SC14CVMDECT SF supports the DECT GAP standard according to EN300 444. For TBR22 type approval (optional) switching off the authentication and encryption is required, which can be done with the VES parameter Tbr\_22.

FINAL

#### 4.10.2 Out-of-Range handling

When the PP goes in-range or out-of-range a signal is sent from the PP to the MMI software indicating whether the PP is in-lock or is out-of-lock with the FP.

#### 4.10.3 Preamble antenna diversity

To optimise the audio quality caused by rapidly changing radio paths (fading), the SC14CVMDECT SF supports preamble antenna diversity. The preamble diversity algorithm uses RSSI measurements to judge the radio signal strength on both antennas and, as a result, the choice of the best performing antenna is determined. This antenna will then be used for the receive slot and the next transmit slot.

The preamble antenna diversity is supported with two antennas. The preamble diversity can be controlled by VES. See document reference [4] and section 4.13 for more information about antenna diversity.

#### 4.10.4 Broadcasting messages

Messages consisting of up to 19 bytes can be broadcasted from FP to all registered PPs. Broadcasting does not require an active connection. Broadcasting does not use retransmission, therefore broadcasting is not secured. If the real time clock is enabled this data is also broadcasted to all PPs.

#### 4.10.5 IWU to IWU messaging

The protocol in the SC14CVMDECT SF module is made according to the DECT/GAP standard as defined in EN 300 175 and EN 300 444.

The DECT standard defines an EMC code (see EN 300 175-5, chapter 7.7.23.). This code is unique for a DECT product and must be programmed by the DECT manufacturer to the correct manufacturer code.

The EMC code must be the same for SC14CVMDECT SF based product families when using the IWU to IWU messaging.

If the Dialog default EMC VES value is changed the IWU to IWU messaging may not operate correctly.

IWU data is transferred in a FA format frame; see chapter 6.1 in EN 300 175-4. This frame has an information field of maximum 63 bytes of which maximum 52 bytes can be used for IWU data. With the SC14CVMDECT SF it is only possible to send 5 frames in a row without pause. The following frame must be an acknowledge-frame to secure that the internal buffers within the SC14CVMDECT SF are emptied.

The FA frame is segmented in 5 byte fragments and transferred over the air-interface in the A-field. The 2-bytes CRC is used to determine if the data is received correctly. If the data is not received correctly this is signalled back to the transmitter by the Q2 bit, and the data is retransmitted.

The FA frame has a 2 bytes checksum, used to determine if the complete packet is received correctly. If A checksum error is signalled back to the transmitter and

the complete packet is retransmitted. The packet will be retransmitted until it is received correctly, or until the link is closed.

More transmitted packets will be received in the same order as they were transmitted. The application must handle flow control, if needed.

#### 4.11 REGISTRATION

The PP and the FP must be paired using a procedure called Registration. Without Registration, the PP will be out-of-lock and will not be able to establish a link to an FP and therefore not be able to make a call. The registration uses the unique product identities and secures the PP and FP to allow no cross-communication.

The PP can be de-registered from an FP either via the FP or PP MMI Software using the command interface. It is also possible to deregister a PP from another registered PP.

It is possible to pair a PP and FP during the production.

# dialog

#### Cordless Voice Module

FINΔI

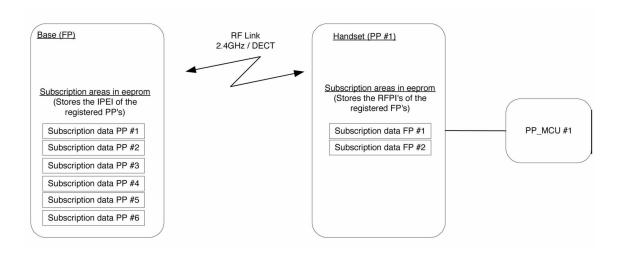

#### 4.11.1 Handling product identities

To secure that the FP and PPs do not make crosscommunications a unique ID must be entered into the VES of an FP or PP. For the DECT version the ID for the FP is named RFPI and for the PP the ID is named IPEI. These numbers are factory settings.

After a successful registration, the IPEI is stored in the FP and the RFPI is stored in the PP. In this way the two

parts are known to each other and are allowed to make connections. The registration data are automatically stored in VES of the FP and PP while making the registration.

It is possible to register the same PP to 2 FPs, but it can only be used in one FP at the same time.

Figure 20: Handling product identities

#### 4.11.2 Deregistration

There are two ways of deregistering a PP from an FP:

- Remote FP and PP deregistration

The correct way to deregister a PP from an FP is to deregister it remotely in the FP. If this is done over a service connection from the PP to the FP, the FP actually performs the deregistration and then it is automatically signalled to the PP which in turn will drop out-of-lock. Using this method it is also possible to deregister other PPs registered to the FP from one PP.

- Removing all registrations at once from the FP (e.g. in case the original PPs are lost).

#### 4.12 PCM INTERFACE

The PCM supports the following modes:

- SLAVE mode clock sync. In this mode the clock of the module will be adjusted to follow the PCM provided by the external PCM master clock. All audio samples are kept if the provided PCM clock accuracy is +/- 5 ppm, which is a DECT radio requirement.

- SLAVE no clock sync. In this mode the clock of the module is not synchronized. This means audio sample will be discarded in case the master PCM clock is faster than the clock of the module or samples will be repeated in case the master PCM clock is slower.

- · MASTER mode. The FP is master on PCM interface

and therefore provides PCM clock and PCM\_FSC to an external device.

#### 4.12.1 PCM Interface for FP

The SC14CVMDECT SF supports PCM interface functionality to connect to an external audio source/destination

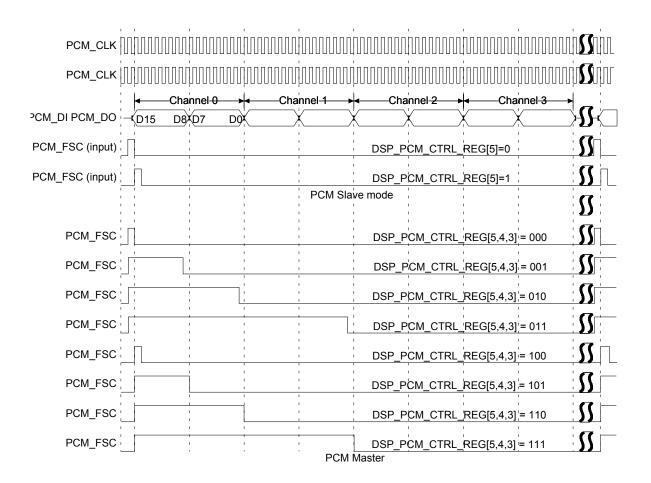

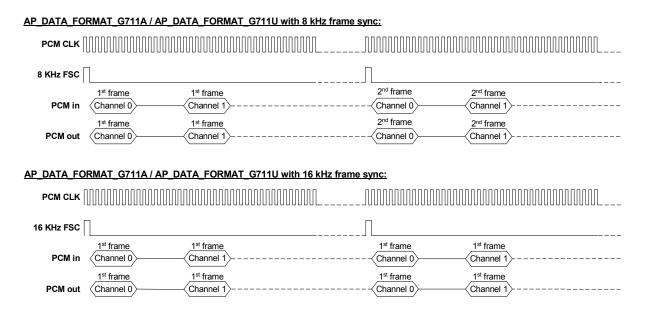

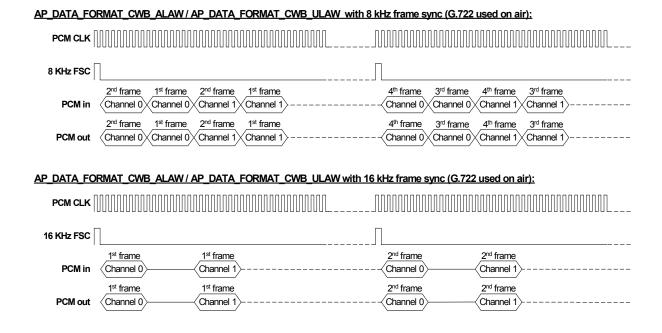

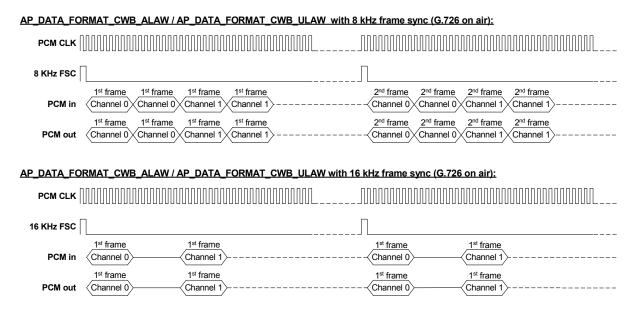

The different PCM interface modes and timings are shown in Figure 21 to Figure 26. Refer to document [1] for detailed information.

#### 4.12.2 PCM\_FSC frequency

The PCM interface supports the following options:

- 8 kHz

- 16 kHz

#### 4.12.3 Length of PCM\_FSC

The PCM interface supports the following options:

- 1: The length of PCM\_FSC pulse is equal to 1 data bit.

- 8: The length of PCM\_FSC pulse is equal to 8 data bits.

- 16: The length of PCM\_FSC pulse is equal to 16 data bits.

- 32: The length of PCM\_FSC pulse is equal to 32 data bits.

# **dialog**SEMICONDUCTOR

#### **Cordless Voice Module**

FINΔI

#### 4.12.4 Start position of FSC

The PCM interface supports the following options:

- The FSC pulse starts 1 data bit before the MSB bit of the PCM channel 0 data.

- The FSC pulse starts at the same time as the MSB bit of the PCM channel 0 data.

#### 4.12.5 PCM clock frequency

The PCM interface supports the following options in master mode:

- 1.152 MHz

- 2.304 MHz

- · 4.608 MHz

- 1.536 MHz

#### 4.12.6 PCM data mode

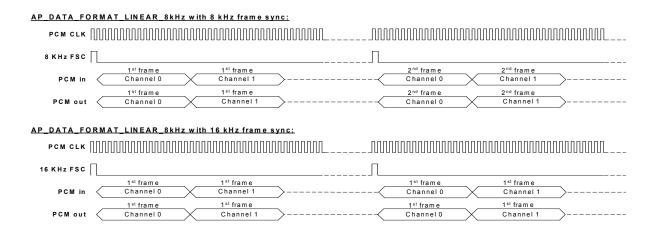

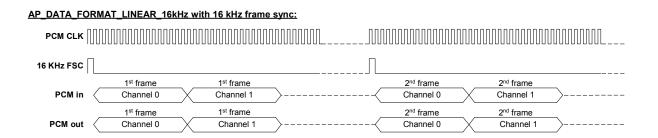

The PCM interface supports the following PCM data formats:

- Linear PCM, 8 kHz sample rate.

Used for narrowband calls (G.726).

- Linear PCM, 16 kHz sample rate. Used for wideband calls (G.722).

- G.711 A-law, 8 kHz sample rate.

Used for narrowband calls (G.726).

- G.711 μ-law, 8 kHz sample rate.

Used for narrowband calls (G.726).

- Compressed wideband using A-law, 16 kHz sample rate. The 16 bit PCM data is encoded as two 8 bit audio samples if 8 kHz frame sync is used. Used for wideband calls (G.722).

- Compressed wideband using μ-law, 16 kHz sample rate. The 16 bit PCM data is encoded as two 8 bit audio samples if 8 kHz frame sync is used. Used for wideband calls (G.722).

Figure 21: PCM interface formats

FINΔI

Figure 22: PCM bus with linear PCM, 8 kHz sample rate

Figure 23: PCM bus with linear PCM, 16 kHz sample rate

FINΔI

Figure 24: PCM bus with G.711 - A-law/μ-law, 8 kHz sample rate

Figure 25: PCM bus with compressed wideband using A-law/  $\mu$ -law, G722 used on air interface

FINΔI

Figure 26: PCM bus with compressed wideband using A-law/ μ-law, G726 used on air interface

#### 4.12.7 PCM Interface for PP

The SC14CVMDECT SF supports PCM interface functionality to connect to an external audio source/destination. Refer to document [2] for detailed information.

- PCM interface mode supports only master mode.

- PCM\_FSC frequency supports 8 kHz and 16 kHz.

- · LENGTH of PCM FSC

The PCM interface supports the following options:

- 1: The length of PCM\_FSC pulse is equal to 1 data bit.

- 8: The length of PCM\_FSC pulse is equal to 8 data bits.

- 16: The length of PCM\_FSC pulse is equal to 16 data bits.

- 32: The length of PCM\_FSC pulse is equal to 32 data bits.

- · Start position of FSC

The PCM interface supports the following options:

- The FSC pulse starts 1 data bit before MSB bit of the PCM channel 0 data.

- The FSC pulse starts at the same time as the MSB bit of the PCM channel 0 data.

- PCM clock

- PCM clock is delivered to an external slave PCM device from SC14CVMDECT SF.

- PCM Data mode

Supports only linear 16 bit PCM.

FINAL

#### **4.13 ANTENNA OPERATION**

Figure 28: One external antenna

Figure 27: Internal circuit of the SC14CVMDECT SF

Figure 27 shows the internal circuit of the SC14CVMDECT SF. Pin RF0 is used for two external antennas and can also be used for RF test purposes. Therefore it is recommended to add a 10 pF capacitor as reserve pattern, even when the two external antennas are not used.

Re-certification of the SC14CVMDECT SF is required if at least one external antenna is added. On request, Dialog Semiconductor can provide a pre-certified PCB layout for an external antenna circuit.

RF1 is also recommended to use and can be connected to the RF cable to be able to do the JPN DECT type approval test.

#### 4.13.1 Internal antenna only

The FAD function is not enabled if only the internal antenna is used. In this case pins RFP0, RFP0n, P0 and P0n must be left unconnected.

#### 4.13.2 Internal and external antenna with FAD

Figure 28 shows one external antenna that is connected to RF1 of the SC14CVMDECT SF. This configuration supports the FAD function. In this case pins RFP0, RFP0n, P0 and P0n must be left unconnected.

# **dialog**

#### **Cordless Voice Module**

### FINAL

## 5.0 CAT-iq

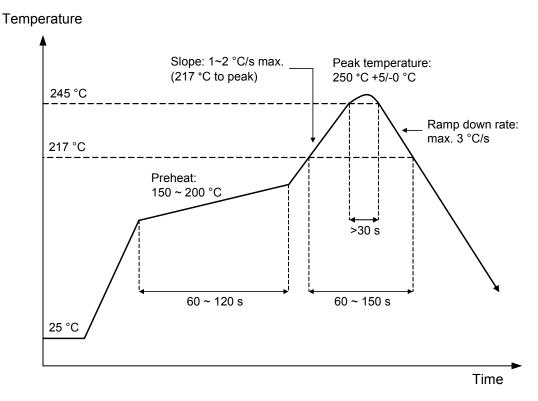

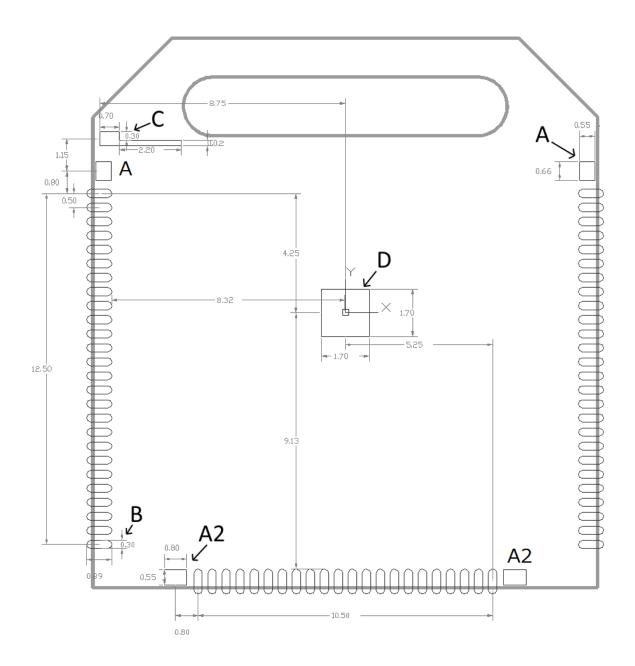

#### **5.1 INTRODUCTION**